This lecture will focus on the Hardware Description Language (HDL), SystemVerilog (SV). You will not learn this HDL by listening at lectures. Instead, you will be learning SV by designing actual circuits and testing them.

Here is a list of things that you will learn in this lecture. Some of the slides are derived or modified from the slides provided by the publisher of the Harris & Harris book. This is another recommended textbook for this module. It is much thinner than the Patterson & Hennessy book, and is a more suitable textbook in many ways to support this module. Unfortunately, our library does not have an electronic copy of H&H for student to borow. If you can acquire a copy of this textbook, I recommend it highly.

| Hardy                                                  | ware description Languages                                                                  |                 |

|--------------------------------------------------------|---------------------------------------------------------------------------------------------|-----------------|

| ✤ Hardware desci                                       | ription language (HDL):                                                                     |                 |

| <ul> <li>Specifies logic full</li> </ul>               | unction only                                                                                |                 |

| <ul> <li>Computer-aided<br/>optimized gates</li> </ul> | design (CAD) tool produces or synthesizes the                                               | е               |

| Most commerci                                          | al designs use HDLs                                                                         |                 |

| Two leading HD                                         | Ls:                                                                                         |                 |

| ► IEEE standard                                        | 1984 by Gateway Design Automation (Verilog)<br>I (1364) in 1995<br>005 (IEEE STD 1800-2009) |                 |

| ► IEEE standard                                        | 1981 by the Department of Defense<br>I (1076) in 1987<br>08 (IEEE STD 1076-2008)            |                 |

| YKC 8 Oct 2024                                         | EIE2 Instruction Architectures & Compilers                                                  | Lecture 2 Slide |

These are the pros and cons of using a HDL instead of schematic to specify digital hardware:

- Flexible & parameterisable

- Excellent input to optimisation & synthesis

- Direct mapping to algorithms

- Excellent for datapaths

- Easy to handle electronically (only needing a text editor)

- × Serial representation

- × May not show overall picture

- × Need good programming skills

- × Divorce from physical hardware

No modern digital integrated circuits or FPGA based designs that are not specified in some sort of HDL from which the final design is synthesized.

For this module, you will learn a particular level of **abstraction** of the processor hardware known as **Register Transfer Level** (RTL). In RTL specifications, all combinational logic are sandwiched between registers controlled by one or more clock signals.

|                                                     | HDL to Gates                                                                    |                                |

|-----------------------------------------------------|---------------------------------------------------------------------------------|--------------------------------|

| Simulation                                          |                                                                                 |                                |

| Inputs applied to                                   | circuit                                                                         |                                |

| <ul> <li>Outputs checked</li> </ul>                 | for correctness                                                                 |                                |

| <ul> <li>Millions of dollar<br/>hardware</li> </ul> | s saved by debugging in simulation inste                                        | ead of                         |

| Synthesis                                           |                                                                                 |                                |

|                                                     | code into a netlist describing the hardw wires connecting them)                 | are (i.e., a list              |

| Physical design                                     | 1                                                                               |                                |

| <ul> <li>Placement, routi</li> </ul>                | ng, chip layout, – not considered in                                            | this module                    |

| IMPORTANT:                                          |                                                                                 |                                |

| When using an HDL, thir appropriate idiom that i    | nk of the <mark>hardware</mark> the HDL should produce<br>mplies that hardware. | , then write the               |

| Beware of treating HDL                              | ike software and coding without thinking of                                     | f the hardware.<br>H&H 171-173 |

| PYKC 8 Oct 2024                                     | EIE2 Instruction Architectures & Compilers                                      | Lecture 2 Slide 4              |

After specifying your hardware in SystemVerilog HDL, you need to make sure that your design works according to specification. Simulation tools such as circuit simulators, Matlab, Mathematica etc. allow users to predict circuits and systems behaviour WITHOUT having to implement the actual electronic system. This saves both time and money. Furthermore, it is very hard to find a bug in a million or billion transistor circuit on a physical chip because there is no easy way to access internal signals. (This statement is not entirely true. There is a technique used called "scan chain" or JTAG, which allows such internal access, but it is not easy to use.)

After simulation, the design is "**translated**" to low level building blocks (such as gates and flops) through a special type of **hardware compiler** to perform **synthesis**. This is the stage at which circuits can be optimized. For example, redundant gates (such as a 2-input NAND gate with one input always 0) are eliminated. Synthesis produces a network of interconnected building blocks, known as the **netlist**. At this stage, the design is still not necessary linked to any technology for implementation.

The netlist is then further processed to produce the final physical design. This final stage involves many steps such as **technology mapping**, **placement**, **routing**, **timing analysis**, **test vector generation**, **test coverage analysis** etc. We will NOT be considering any part of this stage of design in this module.

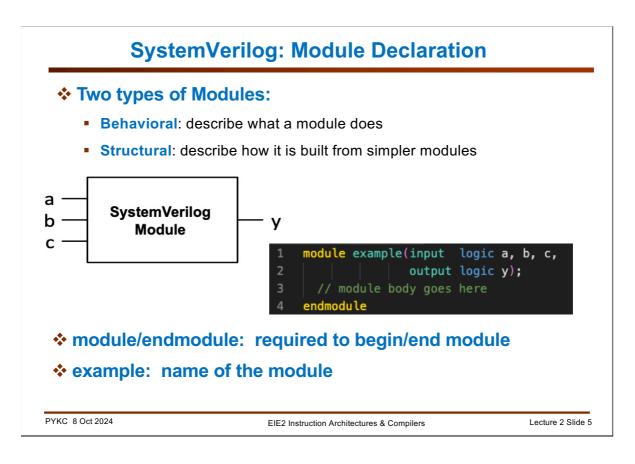

A SystemVerilog design consists of basic units called "**modules**". Each module, like a C function, provides specific functionality. Unlike C functions, modules are not "called" but "**instantiated**". That means that each time you use a module in SV, you "**clone**" a separate entity – the clone has a totally separate existence.

SV is entirely hierarchical. Modules can instantiate other modules.

All modules have inputs and outputs as shown on the slide.

There are many different level of abstractions in specifying a module:

- 1. You can specify something at a **behavioural level** where the SV syntax allows you to describe the abstract functional behaviour rather than physical structure of the hardware.

- 2. Alternatively, you may describe a module in a **structural form**. For example, a top-level (chip level) module may consists of numerous lower-level modules interconnected together.

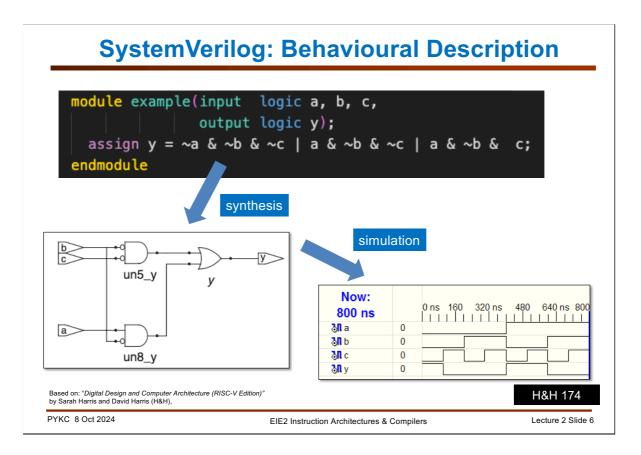

Here is a simple example of a combinational circuit consisting of many Boolean operations described in SV as a Boolean equation. We use the "**assign**" keyword to specify combinational circuit. We then use ~, & and | for NOT, AND and OR Boolean operations respectively.

Sythesis will produce optimized logic as shown in the schematic. Simulation will produce a trace file (i.e. a file contains signal values over time), which can be plotted as timing diagrams.

Here are some basic rules about naming variables in SystemVerilog. It is very much like C or C++.

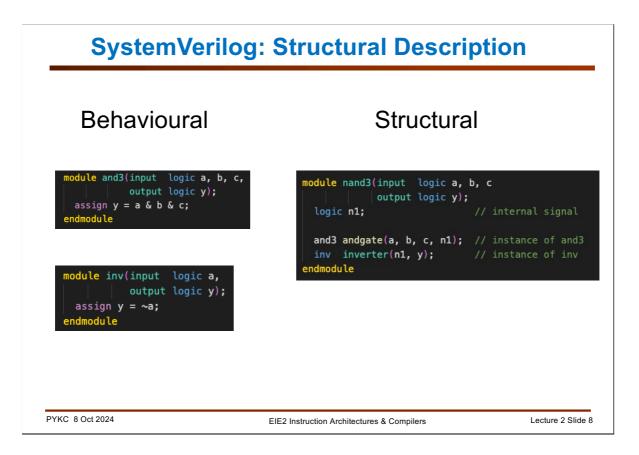

Combinational circuit is easiest to specify using behavioural specification with Boolean operators. You can also choose to provide structural description with interconnected gates as shown on the right.

It is NOT advisable to describe low-level modules in a structural way. It is both tedious, prone to error and not easy to read.

We normally only use structural description when we connect large modules together at a higher level of the design hierarchy.

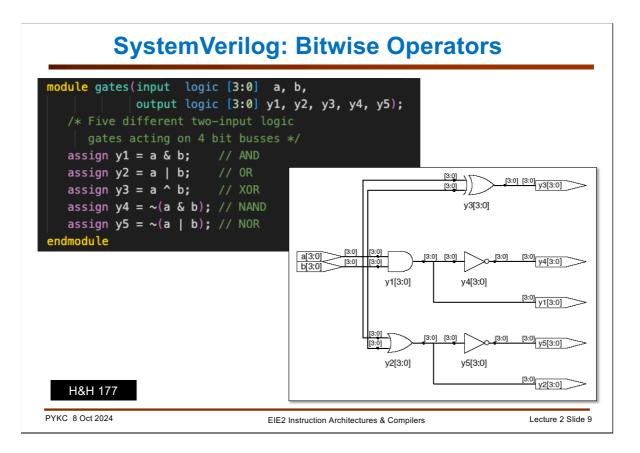

Here is an example where signals are bundled into multi-bit bus. In this case, they are 4-bit wide as [3:0]. SV does not restrict you to name the bus from bit 3 to bit 0. You could declare the signals as, say, [4:1] instead. However, we adapt the notation that LSB is bit 0, and MSB is WIDTH-1, in this case 3.

Now the continuous assignment keyword "assign" results in bit-wise operation. For example:

Means:

y1[3] = a[3] & b[3], y1[2] = a[2] & b[2]. .....

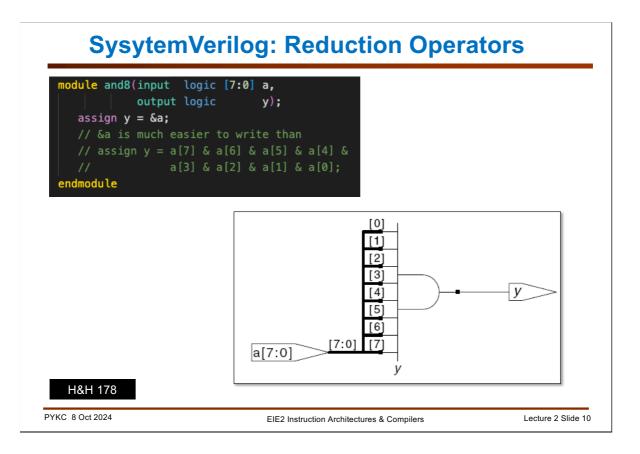

The '&' operator can also be used with a single operand as shown here. This is called a "**reduction**" operator. It reduces multiple bits of a[7:0] to a single bit y. It basically ANDs all bits of a[7:0] together as shown in the slide.

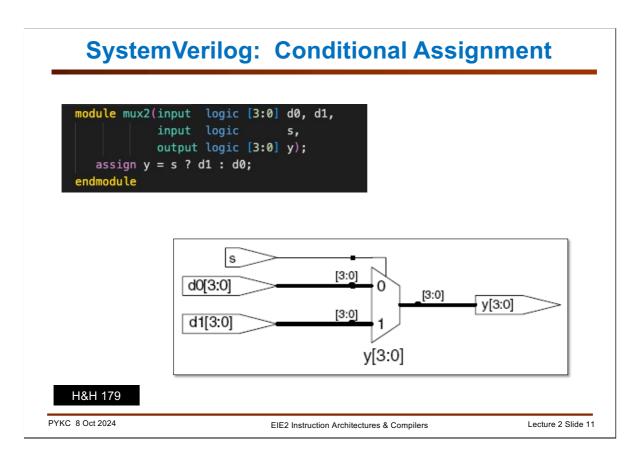

The conditional assignment operator (as found in C or C++) is: cond ? True\_value : False\_value

Therefore, assign y = s ? d1 : d0;

Is the same as: If s is true, y = d1, else y = d0.

This effectively produces a **multiplexer** as shown here.

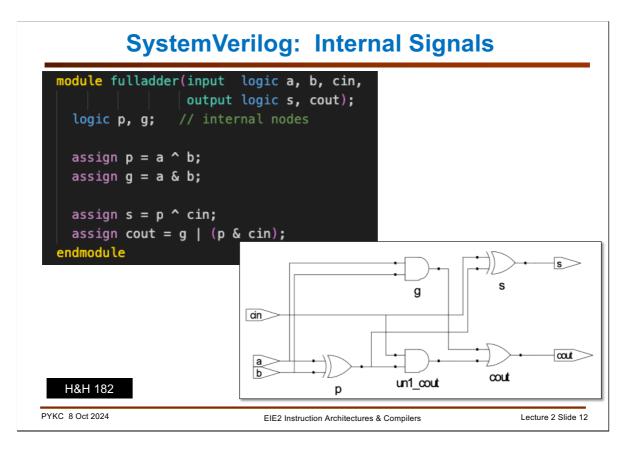

For most modules, there are internal signals which are neither inputs nor outputs. The module here is a single bit full adder. There are two internal signals p, g.

These signals are not "visible" outside the module and are declared as local signals (similar to local variables in C++ functions).

| Highest | ~            | NOT              |  |

|---------|--------------|------------------|--|

|         | *, /, %      | mult, div, mod   |  |

|         | +, -         | add, sub         |  |

|         | <<, >>       | shift            |  |

|         | <<<, >>>     | arithmetic shift |  |

|         | <, <=, >, >= | comparison       |  |

|         | ==, !=       | equal, not equal |  |

|         | &, ~&        | AND, NAND        |  |

|         | ^, ~^        | XOR, XNOR        |  |

|         | , ~          | OR, NOR          |  |

| Lowest  | ?:           | ternary operator |  |

Here are all the operators that SystemVerilog understands. They are listed here with their precedence.

|              | umber of bits, | <b>B</b> = base<br>ecommended (defa | ult is decimal)       |           |

|--------------|----------------|-------------------------------------|-----------------------|-----------|

| Number       | # Bits         | Base                                | Decimal<br>Equivalent | Stored    |

| 3'b101       | 3              | binary 5                            | 5                     | 101       |

| 'b11         | unsized        | binary                              | 3                     | 000011    |

| 8'b11        | 8              | binary                              | 3                     | 00000011  |

| 8'b1010_1011 | 8              | binary                              | 171                   | 10101011  |

| 3'd6         | 3              | decimal                             | 6                     | 110       |

| 6'042        | 6              | octal                               | 34                    | 100010    |

| 8'hAB        | 8              | hexadecimal                         | 171                   | 10101011  |

| 42           | Unsized        | decimal                             | 42                    | 000101010 |

When using SystemVerilog to describe hardware, always remember that you are NOT writing a program. All "variables" are in fact signals. So, when specifying number, beware that you are using physical wire.

Therefore numbers are specified with number of bits explicitly stated. The general format is N'Bxxxx.

N is the number of bits. **B** is the base: b = binary, d = decimal, h = hexadecimal.

See above. If you don't provide bit and base specification, the number is assumed to be 32 bits and in decimal by default. Not specifying the size (i.e. number of bits) of a signal in a design is not recommended.

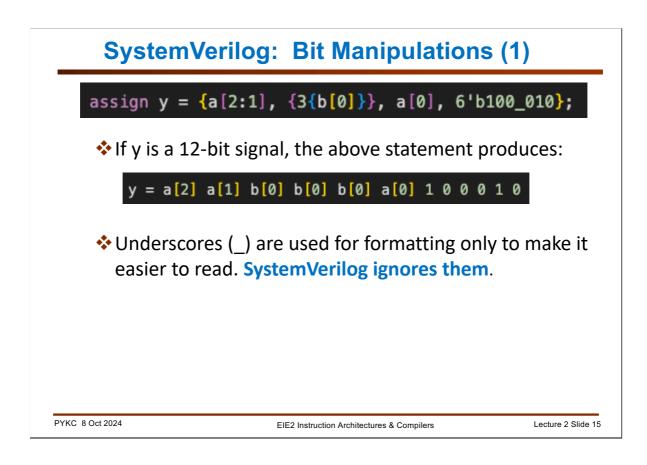

The syntax shown here is very unlike C or C++, and is particularly important to specification of hardware.

$\{ . \}$  is called a **concatenation** operation.  $\{ 1, 0, 1, 1 \}$  forms a 4-bit number 4'b1011.

In the example above, a[2:1] is a two bit number a[2] and a[1].

{ 3 {b[0]} } forms a three bit number with b[0] repeated 3 times.

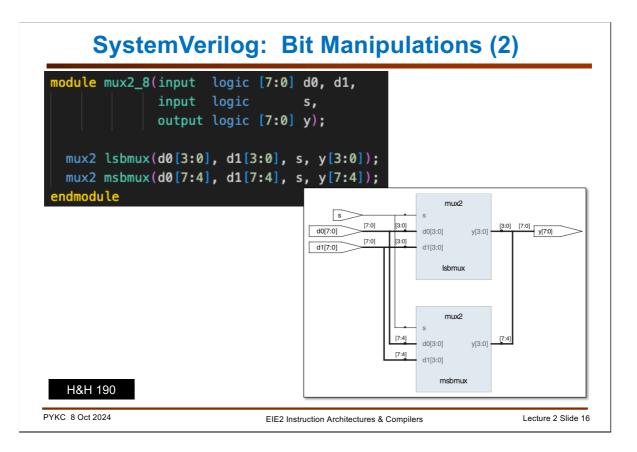

This is an example of slicing and merging different bits of signals d0 and d1 to form an 8-bit output y.

If d0 = 8'b10110101, and d1 = 8'h5A, work out what is y for s = 0, and s = 1?

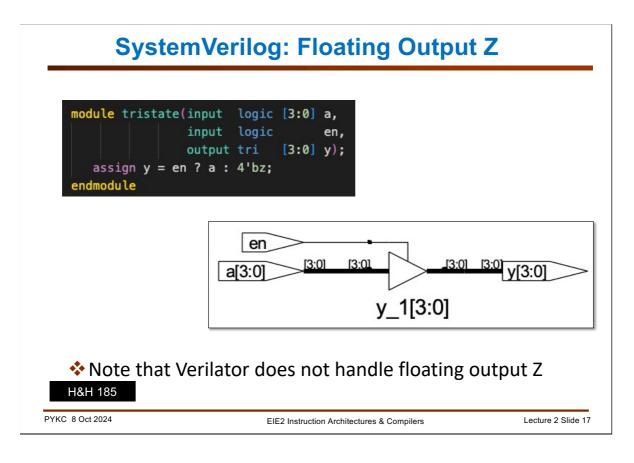

We normally use "**logic**" to specify a signal to be a signal which has values of 0 or 1. However, there is a signal type **tri** which can take on three values: 0, 1, or z, where z is high impedance. This allows SystemVerilog to **describe tri-state outputs**.

In this module, and if en=1, then y = a. If en=0, the output y is tri-state and is therefore not driven by this module.

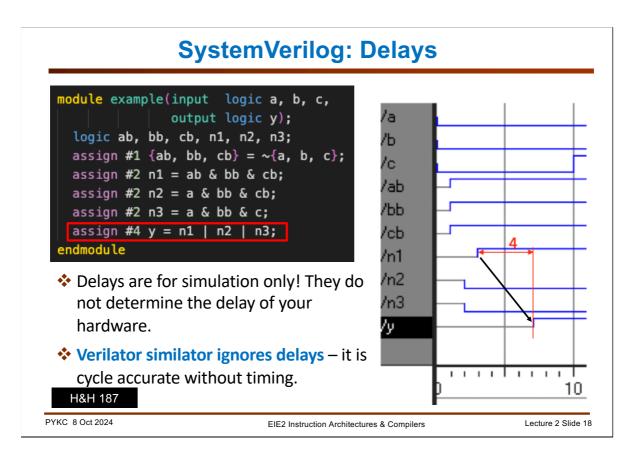

Digital circuits have **delays**. SystemVerilog provides constructs to specify such delays (default in ns). However, Verilator ignores all such specifications: Verilator assumes that all combinational logic output changes immediately with inputs. As such, Verilator is NOT suitable to verify physical digital circuits – it can only be used for functional verification.

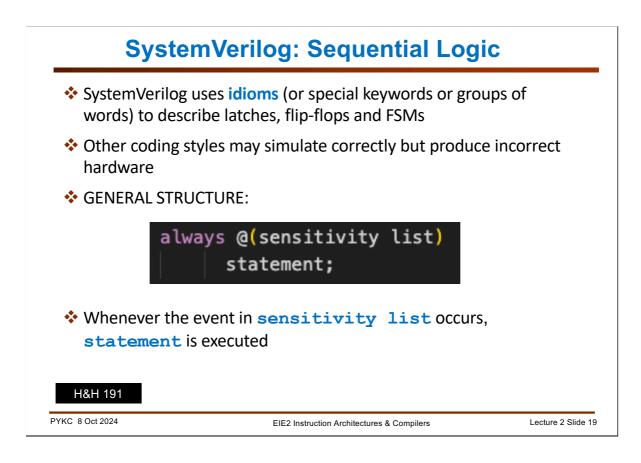

Sequential logics are specified using the pattern:

The "always" followed by @(sensitivity list) means that when any signal in the sensitivity list is asserted, "statement" is executed.

All sequential circuits are described in this form.

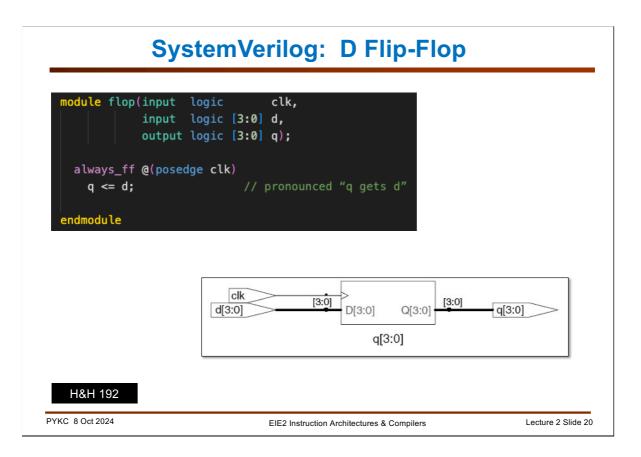

SystemVerilog has a specific syntax for D flip-flops.

## aways\_ff @(posedge clk)

will synthesize one or more registers that are triggered on **positive edge** of the signal **clk**.

Note that you can call your clock signal anything, e.g. **fred** would do equally well. There is NO SIGNIFICANCE in the name itself. However, it is of course advisable to use a signal name that is meaningful.

Note also that the statement to execute in this case is:

q <= d;

This is called **non-blocking assignment** (but don't worry about what it is called for now). The effect of this module is: on rising edge of clk, the 4-bit value of d is transferred to q.

This will synthesize to 4-bit D flip-flop.

| SystemVerilog:                                                                                                                                                                                                                               | Resettable D Flip-Flo                      | ор                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|---------------------------------------------|

| Asynchronous rese                                                                                                                                                                                                                            | et Synchronou                              | s reset                                     |

| <pre>module flopr(input logic cl<br/>input logic re<br/>input logic [3:0] d,<br/>output logic [3:0] q)<br/>// asynchronous reset<br/>always_ff @(posedge clk, posedge r<br/>if (reset) q &lt;= 4'b0;<br/>else q &lt;= d;<br/>endmodule</pre> | eset,<br>;<br>// synchronous reset         | : reset,<br>: [3:0] d,<br>: [3:0] q);<br>:) |

| Clk<br>d[3:0]<br>reset<br>H&H 193                                                                                                                                                                                                            | [3:0]<br>D[3:0] Q[3:0] [3:0]<br>R Q[3:0]   |                                             |

| PYKC 8 Oct 2024                                                                                                                                                                                                                              | EIE2 Instruction Architectures & Compilers | Lecture 2 Slide 2                           |

You should **ALWAYS** add a **reset** control to your flops. Otherwise, your digital system may power up in a random state.

Reset can be implemented as **synchronous** or **asynchronous**. Synchronous reset means that reset happens only on the active edge of the clock signal. Asynchronous reset can happen anytime whenevert the reset signal is asserted and is independent of the clock.

The slide shows the two forms of reset description. For asychonrous case, it also shows how the sensitivity list can **contain multiple conditions**.

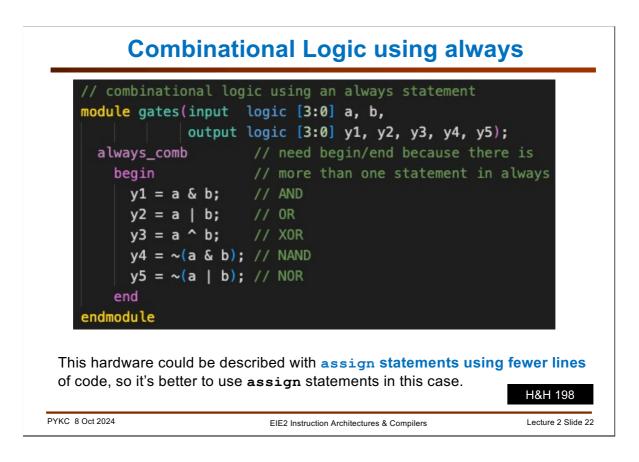

There is a form of **always block** which allows the specification of **combinational circuits**. However, there is no advantage in this form of specification as compare to multiple assign statements.

|            | Combinational Logic using always-case |                |        |                  |             |                                                                                                                                                                                                                                                                  |

|------------|---------------------------------------|----------------|--------|------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| In[30]     | d                                     | 7seg<br>ecoder | out[6  | _                | 0           | <pre>module hex_to_7seg (     output logic [6:0] out,     input logic [3:0] in);     always_comb         case (in)         4'h0: out = 7'b1000000;         4'h1: out = 7'b1111001;         4'h2: out = 7'b0100100;         4'h3: out = 7'b0110000;     } }</pre> |

| in[30]     | out[6:0]                              | Digit          | in[30] | out[6:0]         | Digit       | 4'h4: out = 7'b0011001;                                                                                                                                                                                                                                          |

| 0000       | 1000000                               | 0              | 1000   | 0000000          | 8           | 4'h5: out = 7'b0010010;<br>4'h6: out = 7'b0000010;                                                                                                                                                                                                               |

| 0001       | 1111001                               | 1              | 1001   | 0010000          | 9           | 4 h6: out = 7 b0000010;<br>4'h7: out = 7'b1111000;                                                                                                                                                                                                               |

| 0010       | 0100100                               | 2              | 1010   | 0001000          | B           | 4'h8: out = 7'b0000000;                                                                                                                                                                                                                                          |

| 0011       | 0110000                               | 3              | 1011   | 0000011          | Ь           | 4'h9: out = 7'b0011000;                                                                                                                                                                                                                                          |

| 0100       | 0011001                               | 4              | 1100   | 1000110          | 5           | 4'ha: out = 7'b0001000;<br>4'hb: out = 7'b0000011;                                                                                                                                                                                                               |

| 0101       | 0010010                               | Ś              | 1100   | 0100001          | d           | 4 hb: out = 7 b0000011;<br>4 hc: out = 7 b1000110;                                                                                                                                                                                                               |

| 0110       | 0000010                               | 6              | 1110   | 0000110          | E           | 4'hd: out = 7'b0100001;                                                                                                                                                                                                                                          |

| 0111       | 1111000                               | 7              | 1110   | 0001110          | Ē           | 4'he: out = 7'b0000110;<br>4'hf: out = 7'b0001110:                                                                                                                                                                                                               |

|            | H 199                                 |                | 1111   | 5001110          |             | 4'hf: out = 7'b0001110;<br>endcase<br>endmodule                                                                                                                                                                                                                  |

| PYKC 8 Oct | 2024                                  |                |        | EIE2 Instruction | on Architec | tures & Compilers Lecture 2 Slide 23                                                                                                                                                                                                                             |

A more common use of the **always\_comb** statement is when it is used with the **case** statement.

Here is a 7-segment decoder specification. A 4-bit binary input in[3:0] is decoded to provide 7 output signals to drive a 7-segment display. The outputs are assumed to be **low-active**, i.e. the segments turns ON when the output signals [6:0] are driven LOW.

The function of the decoder can be specified in the truth table shown.

The case statement here shows a direct way to specify such a decoder.

In general, any truth tables or ROMs can be specified in this way.

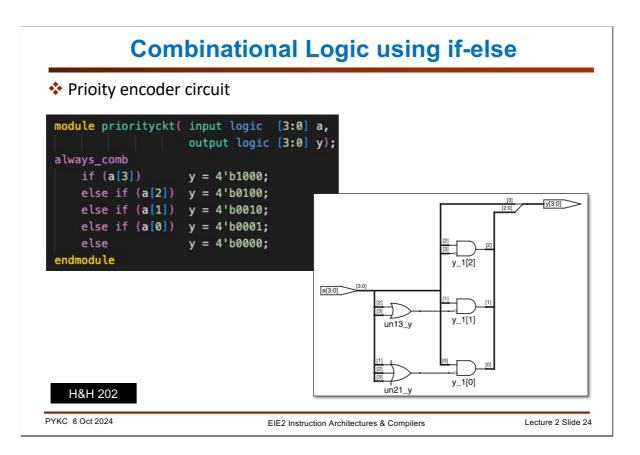

Here is another example called **priority encoder**. **always\_comb** statement uses **if-els**e constructs. The output y[3:0] reports the position of the first '1' in the input from MSB to LSB. So if a[3] is '1', then y[3] is '1' etc.

This is call a **priority encoder** because it detects the highest priority signal being set. The if-else statement is perfect for such description because it fully describes the behaviour of the circuit explicitly.

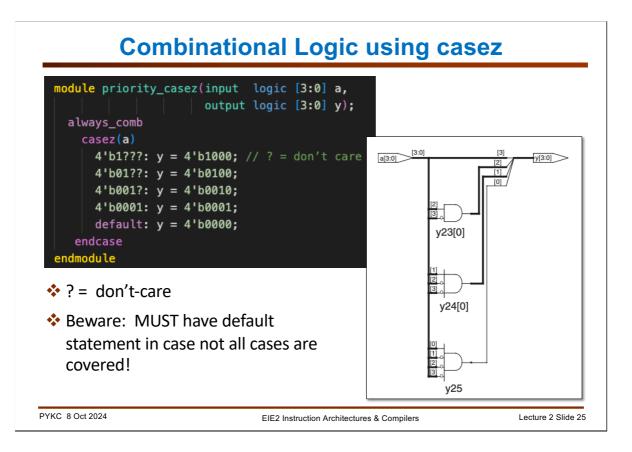

Here is an alternatively method to do the same thing using the casez statement.

Here the conditions are specified with '?' meaning "**don't care**". Note that with 4-bits input, there are 16 possibilities. '?' allows these bit values to be either '0' or '1' (i.e. don't care).

However, beware that not all cases may be covered by such specifidation. You MUST always specify the default case (i.e. when the input a value is not included in the case list).

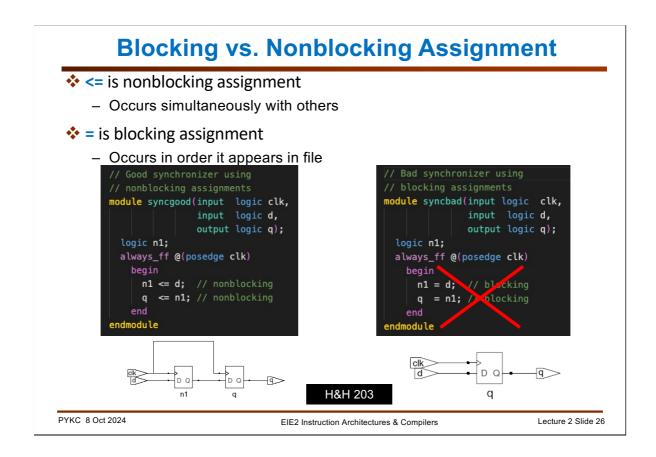

Inside any always block, you should use the **non-blocking assignement** "<=" instead of the **block assignment** "=".

With <=, all assignment statements take effectly ONLY at the end of the always block simultaneously.

With = assignment, assignment occurs sequentially. The synthesized results is a single flip-flop instead of a shift register.

ALWAYS USE "<=" IN YOUR SEQUENTIAL CIRCUIT SPECIFICATION.

| <b>Rules for Signal Assignment</b> |                                                              |               |  |

|------------------------------------|--------------------------------------------------------------|---------------|--|

| Synchronous                        | sequential logic, use:                                       |               |  |

| always_:                           | ff and nonblocking assignments (<=)                          |               |  |

|                                    | always_ff @(posedge clk)<br>q <= d; // nonblocking           |               |  |

|                                    | national logic, use continuous assignme<br>assign y = a & b; | ents (assign) |  |

| * More complic                     | cated combinational logic, use:                              |               |  |

| always_o                           | comb and blocking assignments (=)                            | )             |  |

| Assign a signa<br>assignment S     | al in ONLY ONE always statement or co                        | ontinuous     |  |

|                                    |                                                              |               |  |

Here are some general rules about assingments.